## The CMOS Inverter

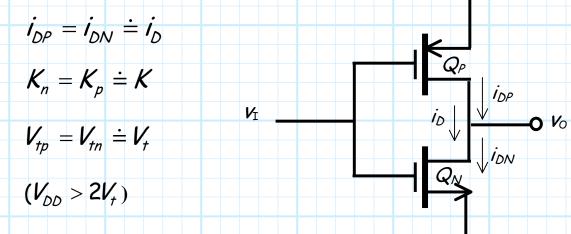

Consider the complementary MOSFET (CMOS) inverter circuit:

In this circuit:

## Q: Why do we call it "Complementary"?

A: Because the device consists of an NMOS and PMOS transistor, each with equal K and equal but opposite  $V_{\tau}$ .

Q: What makes the CMOS inverter so great?

A: Let's analyze the circuit and find out!

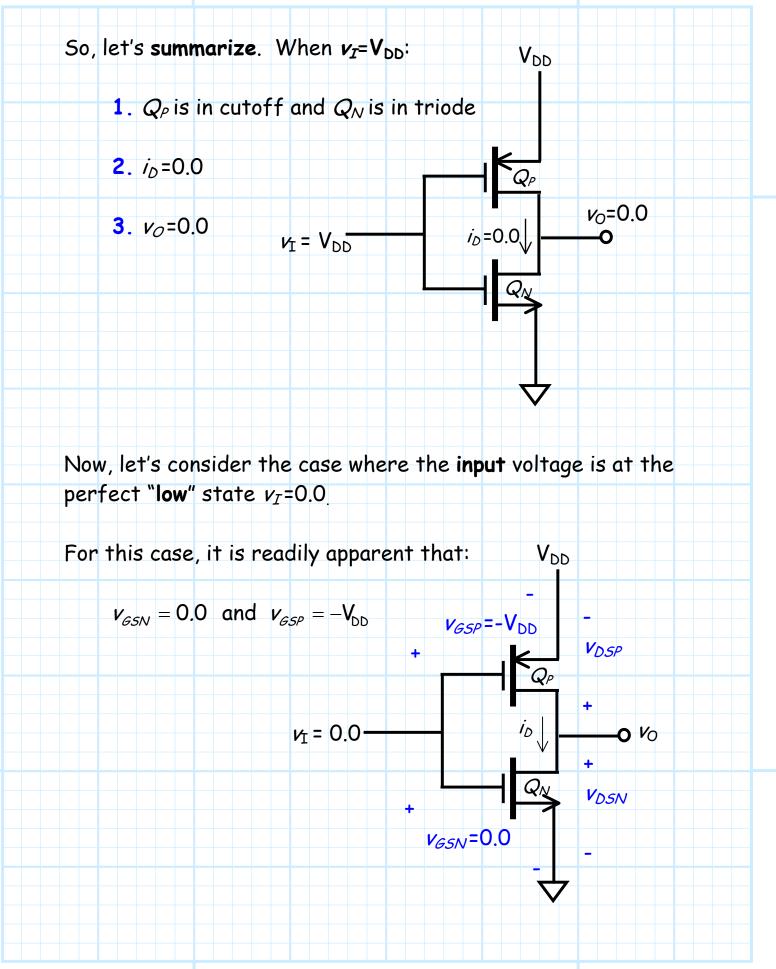

First, let's consider the case where the **input** voltage is at the perfect "**high**" state  $v_I = V_{DD}$ .

For this case, it is readily **apparent** that:

$$v_{GSN} = V_{DD}$$

and  $v_{GSP} = 0.0 V$  +

$$V_{\rm I} = V_{\rm DD}$$

Hence, we can conclude:

$$V_{GSN} = V_{DD} > V_{tn} \rightarrow Q_N$$

has an induced channel !

and:

$$V_{GSP} = 0.0 \text{ V} > V_{tp} \rightarrow Q_P \text{ has } \mathbf{no} \text{ induced channel!}$$

Thus, we can conclude that  $Q_P$  is in **cutoff**, and  $Q_N$  is **either** in saturation or triode.

Let's ASSUME that  $Q_N$  is in **triode**, so we ENFORCE the condition that:

$$i_{D} = K_{n} \left[ 2 \left( v_{GSN} - V_{tn} \right) v_{DSN} - v_{DSN}^{2} \right]$$

$V_{DD}$

VDSP

VD5N

VGSN=VDD

**0** Vo

## Note that:

$$v_{GSN} = v_I = V_{DD}$$

and  $v_{DSN} = v_O$

Therefore:

$$\dot{I}_{D} = K_{n} \left[ 2 \left( V_{GSN} - V_{tn} \right) V_{DSN} - V_{DSN}^{2} \right]$$

$$= K \left[ 2 \left( V_{DD} - V_{t} \right) V_{O} - V_{O}^{2} \right]$$

Now, we actually KNOW that  $Q_P$  is in **cutoff**, so we likewise ENFORCE:

$$i_{D} = 0.0$$

Equating these two ENFORCED conditions, we find that:

$$\dot{i}_{D} = \mathbf{0} = \mathcal{K} \Big[ \mathbf{2} \big( \mathcal{V}_{DD} - \mathcal{V}_{t} \big) \mathcal{V}_{O} - \mathcal{V}_{O}^{2} \Big]$$

Solving, we find that the **output** voltage must be **zero**!

$$v_{0} = v_{DSN} = 0.0 \text{ V}$$

Thus,  $v_{DSN} = 0 < v_{GSN} - V_{tn} = V_{DD} - V_t$ .

$Q_N$  is indeed in the triode mode!

Hence, we can conclude:

$$v_{GSN} = 0.0 < V_{tn} \rightarrow Q_N$$

has **no** induced channel

and:

$$V_{GSP} = -V_{DD} < V_{tp} \rightarrow Q_P$$

has an induced channel!

Thus, we can conclude that  $Q_N$  is in **cutoff**, and  $Q_P$  is either in saturation **or** triode.

Let's ASSUME that  $Q_P$  is in **triode**, so we ENFORCE the condition that:

$$\dot{V}_{D} = \mathcal{K}_{p} \left[ 2 \left( \mathbf{v}_{GSP} - \mathbf{V}_{tp} \right) \mathbf{v}_{DSP} - \mathbf{v}_{DSP}^{2} \right]$$

Note that:

$$v_{GSP} = v_I - V_{DD} = -V_{DD}$$

and  $v_{DSP} = v_O - V_{DD}$

Therefore:

$$i_{D} = K_{p} \left[ 2 \left( V_{GSP} - V_{tp} \right) V_{DSP} - V_{DSP}^{2} \right] \\ = K \left[ 2 \left( V_{t} - V_{DD} \right) \left( V_{O} - V_{DD} \right) - \left( V_{O} - V_{DD} \right)^{2} \right]$$

Now, we actually KNOW that  $Q_N$  is in **cutoff**, so we likewise ENFORCE:

Equating these two ENFORCED conditions, we find that:

$$\dot{I}_{D} = 0.0 = \mathcal{K} \left[ 2 \left( V_{t} - V_{DD} \right) \left( v_{O} - V_{DD} \right) - \left( v_{O} - V_{DD} \right)^{2} \right]$$

Solving, we find that the output voltage must be  $V_{DD}$ !

$$V_{O} = V_{DD}$$

$V_{DD}$

Thus,

$$v_{DSP} = 0 > v_{GSP} - V_{tp} = V_t - V_{DD}$$

.

$Q_P$  is indeed in the triode mode!

So, let's summarize. When  $v_I = 0.0$ :

1.

$$Q_N$$

is in cutoff and  $Q_P$  is in triode

2.  $i_D = 0.0$

3.  $v_O = V_{DD}$

$v_I = 0.0$

$Q_P$

$v_O = V_{DD}$

$v_I = 0.0$

So, the overall behavior of the CMOS inverter is displayed in this **table**:

| VI              | V <sub>O</sub>  | i <sub>D</sub> |

|-----------------|-----------------|----------------|

| 0.0             | V <sub>DD</sub> | 0.0            |

| V <sub>DD</sub> | 0.0             | 0.0            |

Look at what this means! The CMOS inverter provides lots of ideal inverter parameters:

V<sub>OH</sub> = 5.0 V (ideal!)

And since  $i_D$  is **zero** for either state, the **static power** dissipation is likewise **zero**:

This is one of the **most attractive** features of **CMOS** digital logic.